方案 | 简化存储器操作时序,快捷实现FPGA ERAM容量扩展

发布时间2021-01-19

FPGA(Field Programmable Gate Array),现场可编程逻辑器件,具有可多次重复编程,当前FPGA已经发展到具有大容量、高速度SERDES、内嵌ARM等SIP硬核资源,广泛用于视频、通信等多个领域。

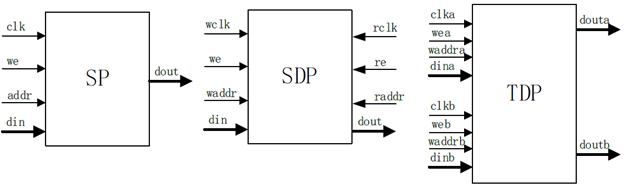

FPGA中常用的ERAM分为以下三种:

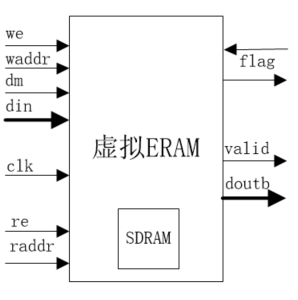

本方案提供一种与ERAM类似的接口,实现64Mb的虚拟ERAM,使用者按照ERAM接口来操作,来实现大数据缓存。

实现的虚拟ERAM具有以下特点:

◆ 接口时序上,使用者不需关心SDRAM器件的时序、激活、预充电、刷新等繁琐操作;

◆ 每次读写操作长度可以支持超长包(65K及以上);

◆ 虚拟ERAM具有随机跳地址读写、数据掩码操作,通过组合,可实现多种灵活的存储方式;

◆ 提供的解决应用方案中,使用的是32bit位宽,64Mb容量的SDRAM,理论带宽为6.4Gbps,实际带宽可以跑6.1Gbps,读写效率在95%以上;

◆方案实现的逻辑资源用量,大约查找表使用242个,寄存器使用533个。可轻量快捷的嵌入到客户工程中;

◆ 时钟频率Fmax可以支持200Mhz以上,基本满足市场上所有SDRAM器件的最大频率;

◆ EG4S可直接使用,外挂时,支可持安路其他系列FPGA器件;

◆ 通过修文件中的宏定义,可以支持市场上不同容量大小,不同接口位宽的SDRAM;

Anlogic的AL3S、EG4S器件,内部集成了64Mb SDRAM,通过上述应用方案,用户不需要额外费时费力编写高效率SDRAM控制器,将FPGA内部的SDRAM当做虚拟ERAM,通过使用BRAM接口的方式访问,快速高效实现数据的花式存储。该应用方案也可支持Anlogic其他系列的FPGA器件。